Upload The Program

FPGA chips are in a way, gigantic RAM devices; on power-down all information is lost and the program that was running before won't be there when power is plugged in again. To fix this, FPGA's have a way of pulling data from a small EEPROM and configuring itsself on power-up. Let's take a look at how to program this EEPROM with an altera .jic file.

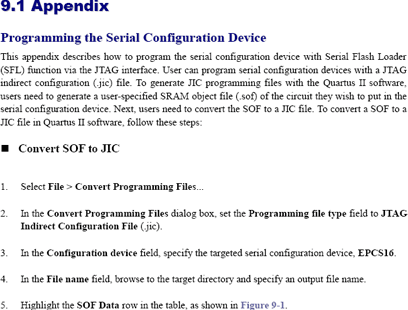

·Terasic's DE0_Nano user guide has a very good step-by-step explaination for how to program the FPGA configuration EEPROM:

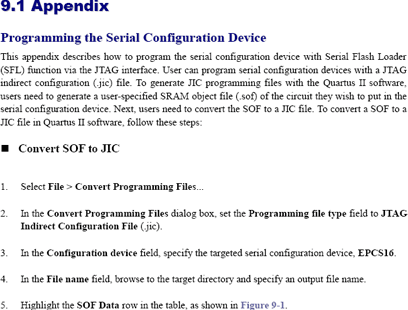

·In Quartus II if you go to File->Convert Programming File you can make the .JIC file necessary for the Altera EEPROM.

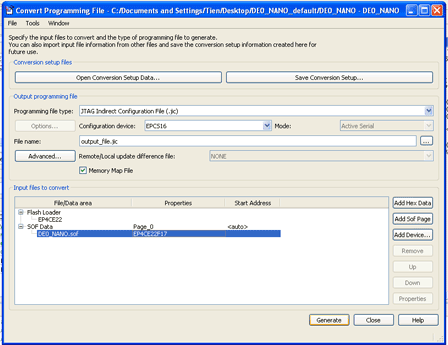

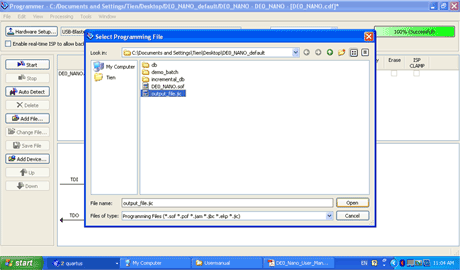

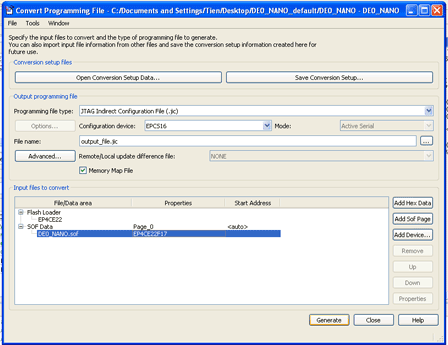

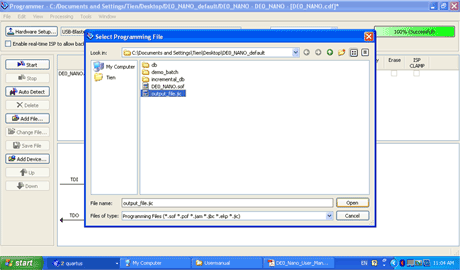

·After you have the output_file.jic, open the Altera programmer (Tools->Programmer) and add the output_file.jic file to the file list:

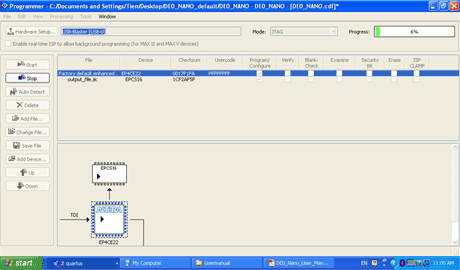

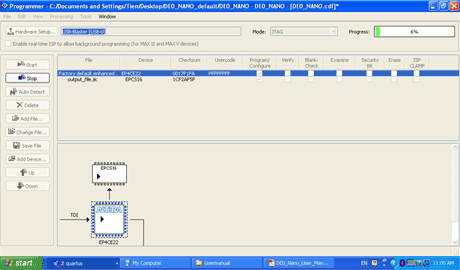

·Then go ahead and click Start and slowly, the EEPROM will get programmed and the status will hit 100%.

·The EEPROM is programmed and now the FPGA code will be loaded into the FPGA upon power-up. Let's give it a test!

FPGA chips are in a way, gigantic RAM devices; on power-down all information is lost and the program that was running before won't be there when power is plugged in again. To fix this, FPGA's have a way of pulling data from a small EEPROM and configuring itsself on power-up. Let's take a look at how to program this EEPROM with an altera .jic file.

·Terasic's DE0_Nano user guide has a very good step-by-step explaination for how to program the FPGA configuration EEPROM:

·In Quartus II if you go to File->Convert Programming File you can make the .JIC file necessary for the Altera EEPROM.

·After you have the output_file.jic, open the Altera programmer (Tools->Programmer) and add the output_file.jic file to the file list:

·Then go ahead and click Start and slowly, the EEPROM will get programmed and the status will hit 100%.

·The EEPROM is programmed and now the FPGA code will be loaded into the FPGA upon power-up. Let's give it a test!